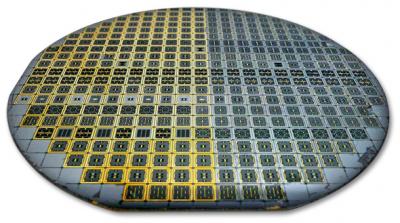

IBM anuncia el primer prototipo de chips SOI de 32 nanómetros

La tecnología SOI (Silicon-on-Insulator) protege mejor a los transistores con una capa de aislante, lo que permite reducir su tamaño, ahorrar energía y mejorar la eficiencia. Los nuevos chips se podrían utilizar tanto en servidores como en electrónica de consumo.

El Gigante Azul ha desarrollado un prototipo de lo que denomina el semiconductor más pequeño, con mayor densidad y rendimiento de la industria.

Estos chips de 32 nanómetros y basados en la tecnología Silicon-on-Insulator (SOI, Silicio sobre aislante), se podrá aplicar a una gran cantidad de desarrollos, desde servidores hasta los incluidos en la electrónica de consumo.

La tecnología SOI protege a los transistores del chip con un relleno de aislante que reduce la fuga de electricidad, ahorrando energía y consiguiendo que la corriente fluya a través del circuito de forma más eficiente, asegura IBM.

IBM ha probado los chips SOI en memoria de acceso aleatorio dinámico (eDRAM), consiguiendo las celdas de memoria más pequeñas de la industria de los semiconductores. La compañía también afirma que los nuevos chips ofrecerán mejor densidad de área, velocidad y capacidad que la memoria de acceso aleatorio estático (SRAM), la cual ya sido anunciada en factores de reducción tanto de 32 como de 22 nanómetros.

De hecho, IBM también está desarrollando esos tamaños junto a otros de sus socios, entre los que destaca AMD, Freescale, STMicroelectronics, Toshiba… El mes pasado anunciaron que acababan de desarrollar las primeras celdas de memoria SRAM capaces de funcionar en tamaños de fabricación de 22 nanómetros.

El desarrollo SRAM es una construcción básica de memoria de alto rendimiento con circuitos complejos como los que se utilizan en los microprocesadores. Los modelos desarrollados en 22 nanómetros utilizan un diseño convencional de 6 transistores y tienen un área de 0,1 micrones cuadrados, tal y como afirma el Gigante Azul.

Mientras tanto, asegura que la tecnología SOI es capaz de ofrecer hasta un 30% de mejora en el rendimiento de los chips, así como una reducción del consumo energético en torno al 40%, comparado con la tecnología tradicional basada en silicio.

Intel, el mayor competidor de IBM en este segmento, ha realizado algunos comentarios al respecto.

“Nuestros prototipos basados en 32 nanómetros ya fueron presentados hace dos años en el IDF y seguimos siendo la única compañía realizando demostraciones que ya funcionan en vez de hablar de tecnología sobre el papel”, ha indicado Megan Langer, portavoz de Intel, en clara referencia al Gigante Azul.

También ha tenido palabras con respecto a la nueva tecnología eDRAM: “Se trata de una tecnología que tanto Intel como otros fabricantes han decidido no utilizar de forma intencionada, ya que tiene un coste muy elevado a la hora de implantarlo y necesita de un mayor número de pasos durante la fabricación”.

Intel no está utilizando eDRAM y tampoco tiene planes de hacerlo por el momento. Actualmente hemos encontrado otras formas de reducir el consumo eléctrico, como es el caso de las puertas lógicas de metal “high-k”, por ejemplo.